icon systems® A TDK Group Company

April 1995

## DESCRIPTION

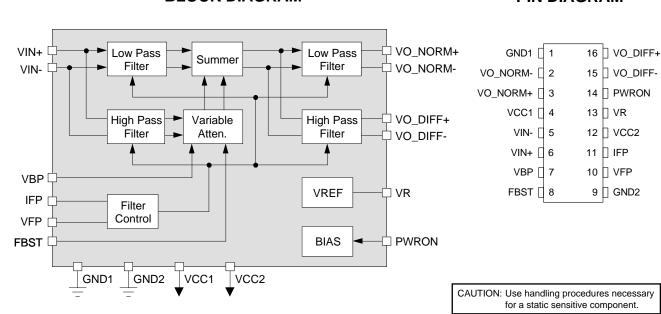

The SSI 32F8030 Programmable Electronic Filter provides an electronically controlled low-pass filter with a separate differentiated low-pass output. A sevenpole. 0.05° Equiripple-type linear phase. low-pass filter is provided along with a single-pole, single-zero differentiator. Both outputs have matched delays. The delay matching is unaffected by any amount of programmed high frequency peaking (boost) or bandwidth. This programability, combined with low group delay variation makes the SSI 32F8030 ideal for use in many applications. Double differentiation high frequency boost is accomplished by a two-pole, lowpass with a two-pole, high-pass feed forward section to provide complementary real axis zeros. A variable attenuator is used to program the zero locations, which controls the amount of boost.

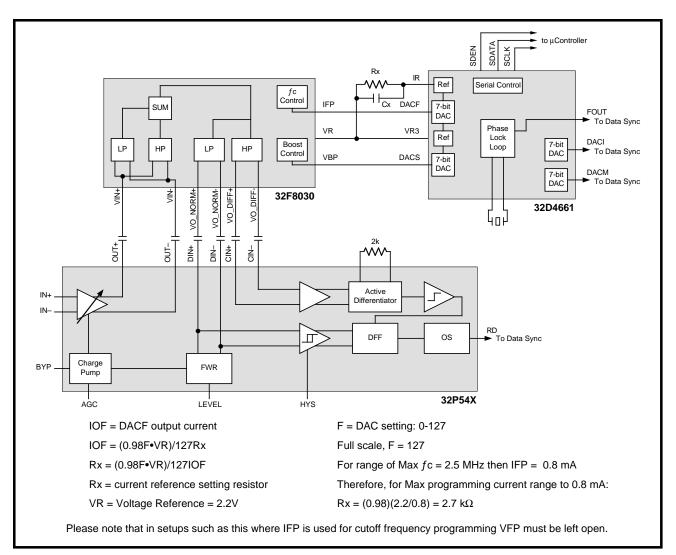

The SSI 32F8030 programmable boost and bandwidth characteristics can be controlled by external DACs or DACs provided in the SSI 32D4661 Time Base Generator. Fixed characteristics are easily accomplished with three external resistors. In addition, boost can be switched in or out by a logic signal.

The SSI 32F8030 requires only a +5V supply and is available in 16-Lead SON, and SOL packages.

## FEATURES

- Ideal for:

- constant density recording applications

magnetic tape recording

- Programmable filter cutoff frequency (fc = 250 kHz to 2.5 MHz)

- Programmable high frequency peaking

(0 to 9 dB boost at the filter cutoff frequency)

- Matched normal and differentiated low-pass outputs

- Differential filter input and outputs

- ±3.0% group delay variation from

0.2 fc to 1.75 fc, 0.25 MHz ≤ fc ≤ 2.5 MHz

- Total harmonic distortion less than 1%

- +5V only operation

- 16-Lead SON, and SOL packages

- 5 mW idle mode

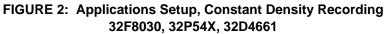

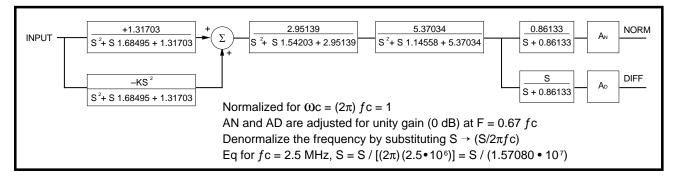

### **BLOCK DIAGRAM**

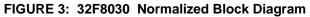

## **PIN DIAGRAM**

### FUNCTIONAL DESCRIPTION

The SSI 32F8030, a high performance programmable electronic filter, provides a low pass 0.05° Equirippletype linear phase seven pole filter with matched normal and differentiated outputs. The device has been optimized for usage with several Silicon Systems products, including the SSI 32D4661 Time Base Generator, the SSI 32P54x family of Pulse Detectors, and the SSI 32P4720 Combo device (Data Separator and Pulse Detector).

#### **CUTOFF FREQUENCY PROGRAMMING**

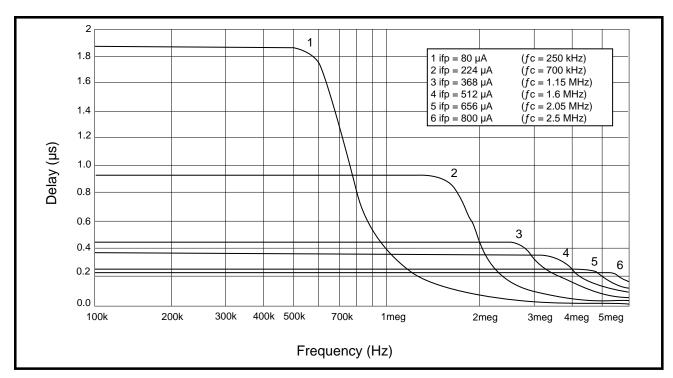

The SSI 32F8030 programmable electronic filter can be set to a filter cutoff frequency from 250 kHz to 2.5 MHz (with no boost).

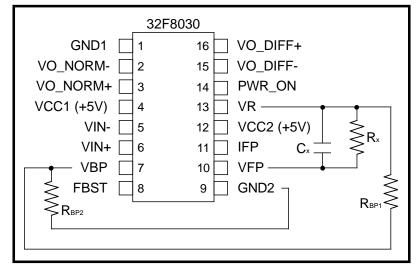

Cutoff frequency programming can be established using either a current source fed into the IFP pin, whose output current is proportional to the SSI 32F8030 output reference voltage VR, or by means of an external resistor tied from the output voltage reference pin VR to pin VFP. The former method is optimized using the SSI 32D4661 Time Base Generator, since the current source into pin IFP is available at the DAC F output of the 32D4661. Furthermore, the voltage reference input is supplied to pin VR3 of the 32D4661 by the reference voltage VR from the VR pin of the 32F8030. This reference voltage is an internally generated bandgap reference, which typically varies less than 1 % over voltage supply and temperature variation. (For the calculations below IVFP = current into IFP or VFP pins).

The cutoff frequency, determined by the -3dB point relative to a very low frequency value (< 10kHz), is related to the current IVFP injected into pin IFP by the formula

Fc (ideal, in MHz) =  $3.125 \cdot IFP = 3.125 \cdot IVFP \cdot 2.2/VR$ , where IFP and IVFP are in mA, 0.08 < IFP < 0.8 mA, and VR is in volts.

If a current source is used to inject current into pin IFP, pin VFP should be left open.

If the 32F8030 cutoff frequency is set using voltage VR to bias up a resistor tied to pin VFP, the cutoff frequency is related to the resistor value by the formula

Fc (ideal, in MHz) =  $3.125 \cdot IFP = 3.125 \cdot 2.2/(3 \cdot Rx)$ where Rx is in k $\Omega$ , & 0.917 k $\Omega$  <Rx<9.17 k $\Omega$ .

If pin VFP is used to program cutoff frequency, pin IFP should be left open.

#### SLIMMER HIGH FREQUENCY BOOST PROGRAMMING

The amplitude of the output signal at frequencies near the cutoff frequency can be increased using this feature. Applying an external voltage to pin VBP which is proportional to reference output voltage VR (provided by the VR pin) will set the amount of boost. A fixed amount of boost can be set by an external resistor divider network connected from pin VBP to pins VR and GND. No boost is applied if pin FBST, frequency boost enable, is at a low logic level.

The amount of boost FB at the cutoff frequency Fc is related to the voltage VBP by the formula

FB (ideal, in dB) =  $20 \log_{10}[1.884(VBP/VR)+1]$ , where 0<VBP<VR.

| PIN DESCRIPT          | PIN DESCRIPTION |                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|-----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                  | TYPE            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| VIN+, VIN-            | I               | DIFFERENTIAL SIGNAL INPUTS. The input signals must be AC coupled to these pins.                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| VO_NORM+,             | 0               | DIFFERENTIAL NORMAL OUTPUTS. The output signals must be AC coupled.                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| VO_NORM-              | 0               |                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| VO_DIFF+,<br>VO_DIFF- | 0               | DIFFERENTIAL DIFFERENTIATED OUTPUTS. For minimum time skew, these outputs should be AC coupled to the pulse detector.                                                                                                                                                                                                                         |  |  |  |  |  |  |

| IFP                   | I               | FREQUENCY PROGRAM INPUT. The filter cutoff frequency FC, is set by an external current IFP, injected into this pin. IFP must be proportional to voltage VR. This current can be set with an external current generator such as a DAC. VFP should be left open when using this pin.                                                            |  |  |  |  |  |  |

| VFP                   | I               | FREQUENCY PROGRAM INPUT. The filter cutoff frequency can be set by programming a current through a resistor from VR to this pin. IFP should be left open when using this pin.                                                                                                                                                                 |  |  |  |  |  |  |

| VBP                   | Ι               | FREQUENCY BOOST PROGRAM INPUT. The high frequency boost is set<br>by an external voltage applied to this pin. VBP must be proportional to voltage<br>VR. A fixed amount of boost can be set by an external resistor divider network<br>connected from VBP to VR and GND. No boost is applied if the FBST pin is<br>grounded, or at logic low. |  |  |  |  |  |  |

| FBST                  | I               | FREQUENCY BOOST. A high logic level or open input enables the frequency boost circuitry.                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| PWRON                 | I               | POWER ON. A high logic level enables the chip. A low level puts the chip in a low power state.                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| VR                    | -               | REFERENCE VOLTAGE. Internally generated reference voltage.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| VCC1, VCC2            | I               | +5 VOLT SUPPLY.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| GND1, GND2            | _               | GROUND                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Operation above maximum ratings may damage the device.

| PARAMETER                          | RATING             |

|------------------------------------|--------------------|

| Storage Temperature                | -65 to +150°C      |

| Junction Operating Temperature, Tj | +130°C             |

| Supply Voltage, VCC1, VCC2         | -0.5 to 7V         |

| Voltage Applied to Inputs          | -0.5 to VCC + 0.5V |

| IFP, VFP Inputs Maximum Current    | ≤1.2 mA            |

#### **RECOMMENDED OPERATING CONDITIONS**

| Supply voltage, VCC1, VCC2 | 4.5 < VCC1,2 < 5.50V |

|----------------------------|----------------------|

| Ambient Temperature        | 0 < Ta < 70°C        |

### **Power Supply Characteristics**

Unless otherwise specified, recommended operating conditions apply.

| PARAM | <b>IETER</b>         | CONDITIONS   | MIN | NOM | MAX | UNIT |

|-------|----------------------|--------------|-----|-----|-----|------|

| ICC   | Power Supply Current | PWRON ≤ 0.8V |     |     | 0.5 | mA   |

| ICC   | Power Supply Current | PWRON ≥ 2.0V |     | 28  | 42  | mA   |

| PD    | Power Dissipation    | PWRON ≥ 2.0V |     | 140 | 231 | mW   |

| PD    | Power Dissipation    | PWRON ≤ 0.8V |     |     | 3   | mW   |

#### **DC Characteristics**

| VIH | High Level Input Voltage | TTL input  | 2.0  | VCC+0.3 | V  |

|-----|--------------------------|------------|------|---------|----|

| VIL | Low Level Input Voltage  |            | -0.3 | 0.8     | V  |

| IIH | High Level Input Current | VIH = 2.7V |      | 20      | μΑ |

| IIL | Low Level Input Current  | VIL = 0.4V | -1.5 |         | mA |

#### **Filter Characteristics**

fc = 1.25 MHz unless otherwise stated

| FCA  | Filter fc Accuracy                            | using IFP pin: IFP = 0.4 mA or<br>using VFP pin: $Rx = 1.84 \text{ k}\Omega$     | 1.125 |     | 1.375 | MHz |

|------|-----------------------------------------------|----------------------------------------------------------------------------------|-------|-----|-------|-----|

| AO   | VO_NORM Diff Gain                             | F = 0.67 fc, FB = 0 dB                                                           | 0.8   |     | 1.20  | V/V |

| AD   | VO_DIFF Diff Gain                             | F = 0.67 fc, FB = 0 dB                                                           | 0.9AO |     | 1.1AO | V/V |

| FBA  | Frequency Boost Accuracy                      | VBP = VR                                                                         | 8.0   | 9.2 | 10.4  | dB  |

| TGDC | Group Delay Variation<br>Without Boost*       | $0.25 \text{ MHz} \le fc \le 2.5 \text{ MHz}$<br>F = 0.2 fc to 1.75 fc           | -3    |     | +3    | %   |

| TGDE | 3 Group Delay Variation<br>With Boost*        | $0.25 \text{ MHz} \le fc \le 2.5 \text{ MHz}$<br>VBP = VR, F = 0.2 fc to 1.75 fc | -3    |     | +3    | %   |

| VIF  | Filter Input Dynamic Range                    | THD = 1% max, F = 0.67 $fc$<br>(no boost, 1000 pF capacitor across Rx)           | 1.0   |     |       | Vpp |

| VOF  | Filter Normal Output<br>Dynamic Range         | THD = 1% max, F = 0.67 $fc$<br>VBP = 0 (1000 pF capacitor across Rx)             | 1.0   |     |       | Vpp |

| VOF  | Filter Normal Output<br>Dynamic Range         | THD = 1% max, F = 0.67 $fc$<br>VBP = VR (1000 pF capacitor across Rx)            | 1.0   |     |       | Vpp |

| VOF  | Filter Differentiated Output<br>Dynamic Range | THD = 1% max, F = 0.67 $fc$<br>VBP = 0 (1000 pF capacitor across Rx)             | 1.0   |     |       | Vpp |

| VOF  | Filter Differentiated Output<br>Dynamic Range | THD = 1% max, F = 0.67 $fc$<br>VBP = VR (1000 pF capacitor across Rx)            | 1.0   |     |       | Vpp |

Filter Characteristics (continued)

| PARAMETER                                                | CONDITIONS                                                                  | MIN | NOM | MAX | UNIT  |

|----------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| RIN Filter Diff Input Resistance                         |                                                                             | 3.0 | 4.0 | 5.0 | kΩ    |

| CIN Filter Diff Input Capacitance*                       |                                                                             |     | 3.0 |     | pF    |

| EOUT Output Noise Voltage*<br>Differentiated Output      | $BW = 100 \text{ MHz}, \text{ Rs} = 50\Omega,$<br>If p = 0.8 mA, VBP = 0.0V |     | 2.7 | 3.2 | mVRms |

| EOUT Output Noise Voltage*<br>Normal Output              | BW = 100 MHz, Rs = 50Ω<br>Ifp = 0.8 mA, VBP = 0.0V                          |     | 1.6 | 2.0 | mVRms |

| EOUT Output Noise Voltage*<br>Differentiated Output      | BW = 100 MHz, Rs = $50\Omega$<br>If p = 0.8 mA, VBP = VR                    |     | 3.1 | 3.8 | mVRms |

| EOUT Output Noise Voltage*<br>Normal Output              | BW = 100 MHz, Rs = $50\Omega$<br>If p = 0.8 mA, VBP = VR                    |     | 1.8 | 2.2 | mVRms |

| EOUT Output Noise Voltage*<br>Differentiated Output      | BW = 10 MHz, Rs = 50Ω,<br>Ifp = 0.08 mA, VBP = 0.0V                         |     | 1.8 | 2.1 | mVRms |

| EOUT Output Noise Voltage*<br>Normal Output              | BW = 10 MHz, Rs = 50Ω<br>Ifp = 0.08 mA, VBP = 0.0V                          |     | 1.0 | 1.2 | mVRms |

| EOUT Output Noise Voltage*<br>Differentiated Output      | BW = 10 MHz, Rs = $50\Omega$<br>If p = 0.08 mA, VBP = VR                    |     | 2.0 | 2.5 | mVRms |

| EOUT Output Noise Voltage*<br>Normal Output              | BW = 10 MHz, Rs = $50\Omega$<br>If p = 0.08 mA, VBP = VR                    |     | 1.1 | 1.5 | mVRms |

| IO- Filter Output Sink Current                           |                                                                             | 1.0 |     |     | mA    |

| IO+ Filter Output Source Current                         |                                                                             | 2.0 |     |     | mA    |

| RO Filter Output Resistance**                            | Sinking 1 mA from pin                                                       |     |     | 70  | Ω     |

| * Not directly testable in production<br>** Single ended | n, design characteristic.                                                   |     |     |     |       |

#### **Filter Control Characteristics**

| VR              | Reference Voltage Output           | 2.0 | 2.40 | V  |

|-----------------|------------------------------------|-----|------|----|

| $I_{_{\rm VR}}$ | Reference Output<br>Source Current |     | 2.0  | mA |

FIGURE 1: Typical Normal/Differentiated Output Group Delay Response

FIGURE 1: 32F8030 Applications Setup 16-Pin SO

VR = 2.2V

VFP = .667 VR

IVfp range: 0.08 mA to 0.8 mA (0.25 MHz to 2.5 MHz)

IVfp = .33VR/Rx

Cx = 1000 pF needed for THD at low fc

VFP is used when programming current is set with a resistor from VR. When VFP is used IFP must be left open.

#### TABLE 1: 32F8030 Frequency Boost Calculations - K = 1.31703 (10<sup>BOOST (dB)/20</sup> -1)

| Assuming 9.2 dB boost for<br>VBP = VR                                                   | Boost                                | к                                    | VBP/VR                                                   | Boost                                   | К                            | VBP/VR                                                   |

|-----------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|----------------------------------------------------------|-----------------------------------------|------------------------------|----------------------------------------------------------|

| $\frac{\text{VBP}}{\text{VR}} \cong \frac{\left(10^{(\text{FB/20})}\right) - 1}{1.884}$ | 1 dB<br>2 dB<br>3 dB<br>4 dB<br>5 dB | 0.16<br>0.34<br>0.54<br>0.77<br>1.03 | 0.065<br>0.137<br>0.219<br>0.310<br>0.413                | 6 dB<br>7 dB<br>8 dB<br>9 dB            | 1.31<br>1.63<br>1.99<br>2.40 | 0.528<br>0.657<br>0.802<br>0.965                         |

| or,                                                                                     |                                      | VBP/VR                               | Boost                                                    | VBF                                     | P/VR                         | Boost                                                    |

| boost in dB=20log $\left[1.884\left(\frac{VBI}{VR}\right)\right]$                       | $\left[\frac{P}{2}\right] + 1$       | 0.1<br>0.2<br>0.3<br>0.4<br>0.5      | 1.499 dB<br>2.777 dB<br>3.891 dB<br>4.879 dB<br>5.765 dB | 000000000000000000000000000000000000000 | .6<br>.7<br>.8<br>.9<br>.0   | 6.569 dB<br>7.305 dB<br>7.984 dB<br>8.613 dB<br>9.200 dB |

#### **TABLE 2: Calculations**

| Typical change in               | Boost (dB) | Gain @ fc(dB) | Gain @ peak(dB) | fpeak/fc | f-3 dB/ <i>f</i> c |

|---------------------------------|------------|---------------|-----------------|----------|--------------------|

| <i>f</i> -3 dB point with boost | 0          | -3            | 0.00            | no peak  | 1.00               |

|                                 | 1          | -2            | 0.00            | no peak  | 1.21               |

|                                 | 2          | -1            | 0.00            | no peak  | 1.51               |

|                                 | 3          | 0             | 0.15            | 0.70     | 1.80               |

|                                 | 4          | 1             | 0.99            | 1.05     | 2.04               |

|                                 | 5          | 2             | 2.15            | 1.23     | 2.20               |

|                                 | 6          | 3             | 3.41            | 1.33     | 2.33               |

|                                 | 7          | 4             | 4.68            | 1.38     | 2.43               |

|                                 | 8          | 5             | 5.94            | 1.43     | 2.51               |

|                                 | 9          | 6             | 7.18            | 1.46     | 2.59               |

Notes: 1. fc is the original programmed cutoff frequency with no boost

2. f-3 dB is the new -3 dB value with boost implemented

3. fpeak is the frequency where the magnitude peaks with boost implemented

i.e., fc = 2.5 MHz when boost = 0 dB

if boost is programmed to 5 dB then f-3 dB = 5.5 MHz

*f* peak = 3.075 MHz

### PACKAGE PIN DESIGNATIONS

(Top View)

#### Thermal Characteristics: θjA

| 16-lead SON (150 mil) | 105° C/W |

|-----------------------|----------|

| 16-lead SOL (300 mil) | 100° C/W |

CAUTION: Use handling procedures necessary for a static sensitive component.

## **ORDERING INFORMATION**

| PART DESCRIPTION      | ORDER NUMBER | PACKAGE MARK |

|-----------------------|--------------|--------------|

| 16-lead SON (150 mil) | 32F8030-CN   | 32F8030-CN   |

| 16-lead SOL (300 mil) | 32F8030-CL   | 32F8030-CN   |

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680-7022 (714) 573-6000, FAX (714) 573-6914